Hausdorff Center for Mathematics

Bonn is an internationally renowned center for mathematical research and teaching. The Hausdorff Center for Mathematics (HCM), established in 2006 as the first German Cluster of Excellence in Mathematics, is a major center for mathematical research and international scientific exchange. Its spectrum ranges from pure and applied mathematics to interdisciplinary research, including theoretical economics. HCM features the Hausdorff Research Institute (HIM) with its trimester programs, the Hausdorff school (HSM) which mainly addresses postdocs, and our graduate school (BIGS) for PhD students.

Intro

Further Links

Fields Medalists

Leibniz Prizes

News and Highlights

They are the best young German female mathematicians: At the European Girls' Mathematical Olympiad 2024 (EGMO) in Tskaltubo (Georgia), the German team won one gold and two silver medals. A total of 212 young people from 54 countries took part in the top international tournament for mathematically talented school girls. As every year, the German team was supported by the HCM and assisted on site by female PhD students from Bonn.

Many kidney diseases are manifested by protein in the urine. However, until now it was not possible to determine whether the protein excretion is caused by only a few, but severely damaged, or by many moderately damaged of the millions of small kidney filters, known as glomeruli. Researchers at the University Hospital Bonn, in cooperation with mathematicians from the University of Bonn, have developed a new computer method to clarify this question experimentally. The results of their work have now been published as an article in press in the leading kidney research journal "Kidney International".

The Carl Friedrich von Siemens Foundation awards the Heinz Gumin Prize for Mathematics to Don Zagier, Director Emeritus at the Max Planck Institute for Mathematics in Bonn and Associate Member of the Hausdorff Center for Mathematics. The Foundation hereby honors the prizewinner's groundbreaking research work on number theory and the theory of modular forms. At 50,000 euros, the Gumin Prize is the most highly endowed mathematics prize in Germany. The award ceremony will take place in mid-May 2024 at the Carl Friedrich von Siemens Foundation.

The Department of Mathematics (Fachgruppe Mathematik) honors Thorsten Michael Beckmann with the Hausdorff Memorial Prize for the best dissertation of the academic year 2022/2023 in mathematics. The honor today was presented by the chair of the Department, Herbert Koch, before the Hausdorff Colloquium in the Lipschitz Hall.

Hausdorff Chairs

The Hausdorff Chairs make it possible to complement the faculty without the usual constraints in terms of timing and fields. We seek internationally outstanding scientists who fit into the broad spectrum of the Hausdorff Center.

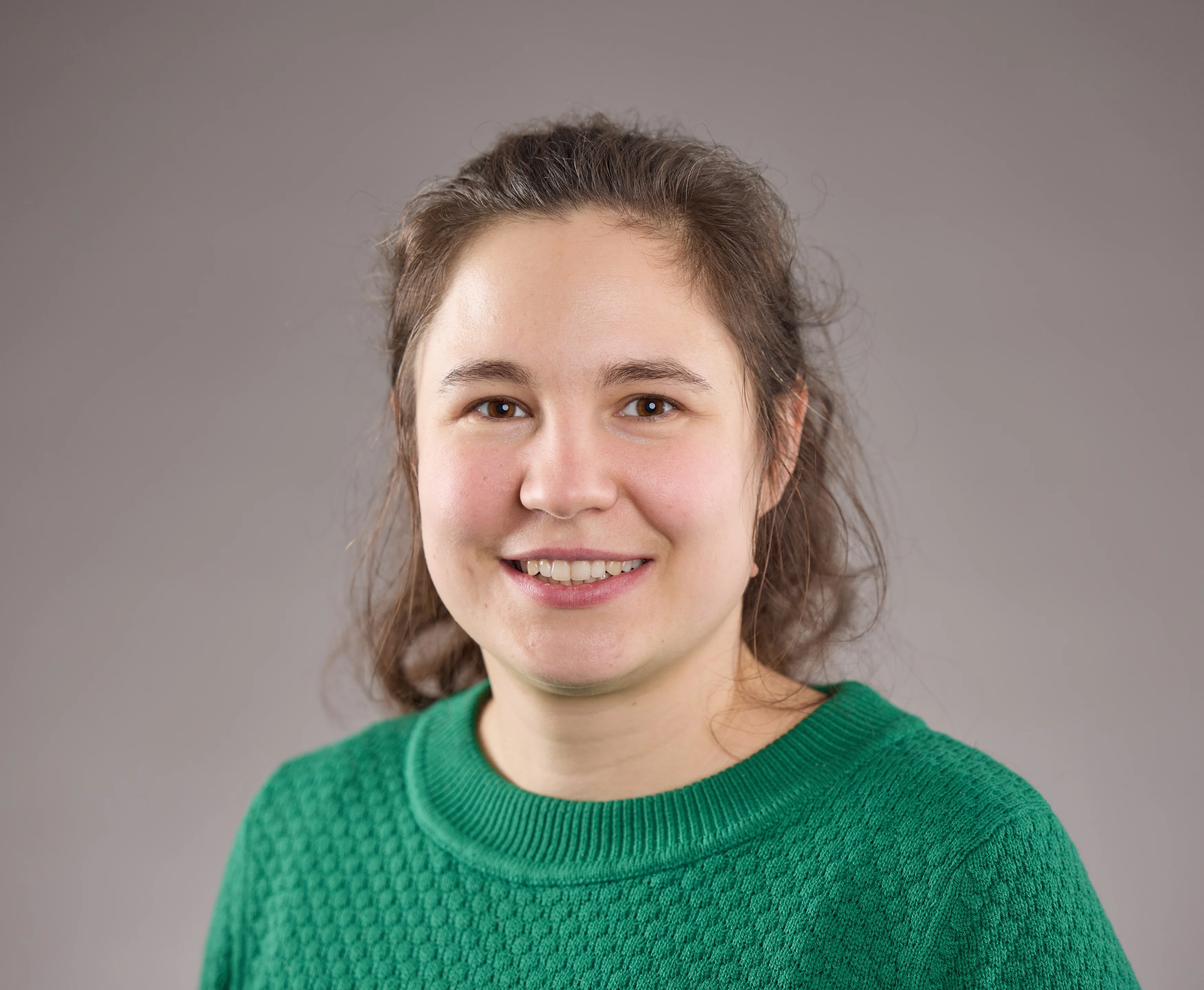

Angkana

Rüland

Stefan

Müller

Sven

Rady

Lisa

Sauermann

Christoph

Thiele

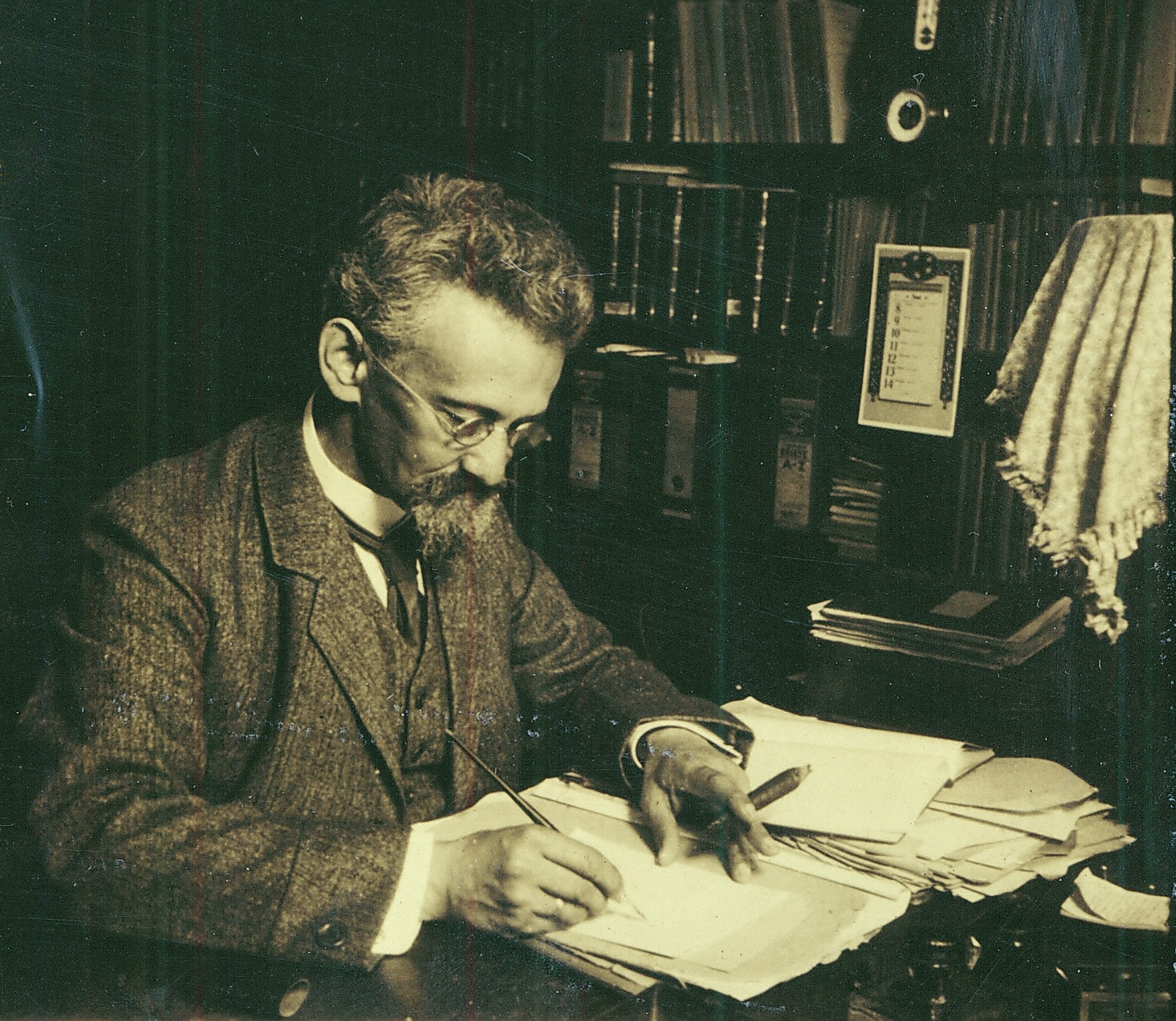

Felix Hausdorff

The center is named after the famous mathematician Felix Hausdorff. Felix Hausdorff was born on 8 November 1868 in Breslau as the son of a Jewish merchant. He was appointed associate professor in Bonn in 1910 and assumed a full professorship in 1913 in Greifswald. He returned to Bonn in 1921 to continue his work until 1935. During the national socialist regime, he suffered increasing harassment and humiliation until 26 Januar 1942, when he and his wife chose suicide over imminent deportation to a concentration camp. With his masterpiece Grundzüge der Mengenlehre (1914), Hausdorff established topology as an independent discipline in mathematics. In addition, Hausdorff made significant contributions to general and descriptive set theory, measure theory, algebra, functional anaylsis, probability theory, and insurance mathematics.

Bonn Junior Fellows

The BJF program offers attractive positions in an outstanding scientific environment to excellent researchers at an early stage of their careers. It provides a springboard to prestigious permanent positions worlwide.